随着AI技术快速发展、高清视频及自动驾驶等应用不断普及,对于高性能计算的需求也在提速。相关标准组织同样加快了新标准的推出,其中高性能计算机的供电电源在供电能力、输出接口等参数上也在不断提升。Intel在2022年推出了ATX3.0标准,在电源的峰值功耗方面要求提升巨大。电源整体输出能力需具备100ms承担120%额定功率输出、10ms承担160%额定功率输出、1ms承担180%额定功率输出、100μs承担200%额定功率输出。

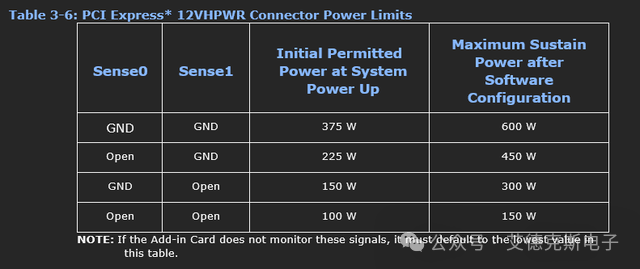

同时PCIe5.0采用16Pin接口,其中4Pin用于通讯,12Pin用于供电,每Pin最大承载电流在9.2A,最大可以输出600W供电接口。

图一 PCIe 12V接口功率限值

直流电子负载可用来测试电源的输出特性,除了按照额定电压及最大功率需求选择电子负载规格外,还需要考虑速度的指标以保证达到电源动态响应测试的要求。在这一测试中直流电子负载的电流上升速度至少要达到5A/μs。

图二 PCIe 12V接口电流上升速率

随着电子技术的日益发展,对电子负载的要求也变得越来越高,除了高性能计算机电源外还有很多高电流变化率的应用场景。如何提供成熟稳定的产品帮助用户实现尖端的测试需求,考验着电子负载制造商的“硬实力”。

艾德克斯新品IT8700P+系列高速多通道直流电子负载采用机框加模组形式,单机最多16通道支持多通道测试,亦可通多主从并机扩展功率。具备高速动态响应,单模组最大上升速度12A/μs,可实现电流最小上升时间< 10μs。单机可实现48A/μs最大上升速度。同时更低的导通内阻适合低压带载测试。更快的环路速度,可精准控制电流无过冲,提高测试效率。适合于高速电源、超级电容、燃料电池、锂电池、太阳能电池的测试。

图三 IT8733P+CC电流实测12A/μs

动态测试:0.01s,50%,A=1A,B=120A

除了电子负载本身需具有高速的硬件指标,测试线接线方案也影响着测试的实际效果。根据法拉第电磁感应定律,一个变化的磁场会在导线上产生一个感应电动势(电压)。当电流尝试在很短的时间内发生较大的变化时,导线的电感会产生一个与电流变化方向相反的感应电动势,从而阻碍这种电流变化。因此当电流变化较大时,由于导线的电感性,会在导线上产生较大的压降。这就是为什么在高速数字电路、射频电路和电力传输中,电感效应是非常重要的考虑因素。在这些应用中,导线、电路板走线甚至元件的布局都可能成为关键因素,因为它们都可能引入不希望的电感效应。

导线的电感效应

我们用具体测试带大家认识一下导线的电感效应。如图四所示,测试电源采用ITECH大功率直流电源IT6532D(6V/60A),后端采用长导线连接ITECH多通道直流电子负载IT8732P+(机框:IT8702P),可以看到长导线电感大导致的直流电阻大,负载端电压瞬间下降5.5V至0.5V左右,此时由于电压过低,负载呈现饱和状态,虽然负载具有优秀的动态速度但因导线原因会有电流过冲。

图四 6A/μs恒流35A长导线

通道1:电流,通道2:负载端口电压

当使用优化的导线接线替代长导线,在同样的测试条件下,我们可以看到如图二所示,电压下降4V至2V左右,此时负载IT8732P+可以迅速带载并无电流过冲。所以在客户需要较大电流变化率的场合,建议更换低电感导线,这样才能得到完美低干扰的测试数据,也能保护待测物不受过冲电流的冲击。

图五、短导线实测效果

如何减小导线的电感效应?

降低外接正负导线的电感性是电子设计中的常见考虑。以下是一些建议和方法,用于减小导线的电感效应:

1、缩短导线长度:电感与导线的长度成正比。缩短导线的长度可以直接降低其电感。

2、使用更宽的导线:导线的电感与其尺寸和形状有关。较宽的导线具有较低的电感。

3、使用并联导线:多根并行的导线可以分担电流,并且总的电感会下降。

4、优化布线:将正负导线并行放置并靠得很近,可以使得它们的磁场相互抵消,从而降低总的电感。

5、使用屏蔽或同轴电缆:这些电缆的设计可以将中心导体和外层屏蔽间的电感降至最低。

6、使用低电感设计的连接器和端子:市场上有些连接器和端子被设计为具有低电感特性,适用于高频或高速应用。

7、添加去耦电容:在电源和负载之间添加去耦电容可以提供一个低阻抗的路径,对于高频信号或电流尖峰来说,这可以降低电感的影响。

对于特定的应用或特定的条件,可能需要采用一种或多种策略组合以达到最佳效果。ITECH艾德克斯具有丰富的行业经验,可为用户的不同测试提供及时的技术指导及成套方案。